-

Broj sadržaja

40390 -

Na DiyAudio.rs od

-

Broj dana (pobeda)

602

Content Type

Profiles

Forum

Blog

Kalendar

Sve objavljeno od Zen Mod

-

mda, umatchovao turu JFets danas, tako da je to sutraske polemljeno ........ PE vidis u sredu, kontam

-

-

-

znam ja jednog jos ce ti i kavudve skuva, da ceifis dok olajavamo ninju

-

-

Babelfish XA252 / Babelfish XA252 SIT/ Babelfish XA252 SET

Zen Mod je odgovorio/la Zen Mod's temus u Solid State

ene, napravljen je i SissySIT R.4 promene su - jos stabilniji Iq u dinamickom rezimu, kao i kompletna DC sprega input-output primenljivo za sve skorasnje ampove sa identicnim FE no sacekacu jedno godinu dana sa objavom, dovoljno sam se u nogu upucao vec sad .... sta - nogu ..... obe noge ...... -

Babelfish XA252 / Babelfish XA252 SIT/ Babelfish XA252 SET

Zen Mod je odgovorio/la Zen Mod's temus u Solid State

pominjanje "najboljeg" mi izaziva osmeh, dok cekam da se brew prva jutarnja to ti je kao da kontempliras koja je zena najbolja ....... dok ti ova sprema rucak a deca koju ti je rodila ti ili skacu po glavi ili ih izvlacis pijane iz kafica W. mi svedok ( bar za 2) - ovo su prakticno 3 razlicita ampa ......... osnovni kvalitet im je zajednicki, a razlike prave distinkciju na nivou licnih preferenci i ukusa dakle ........... pominjanje "najboljeg" mi izaziva osmeh, eo vec se brew prva jutarnja -

Babelfish XA252 / Babelfish XA252 SIT/ Babelfish XA252 SET

Zen Mod je odgovorio/la Zen Mod's temus u Solid State

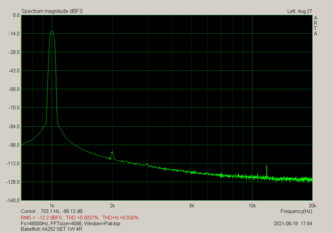

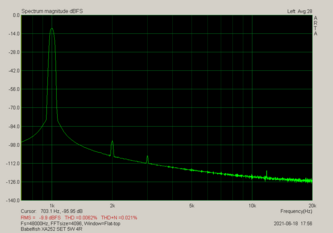

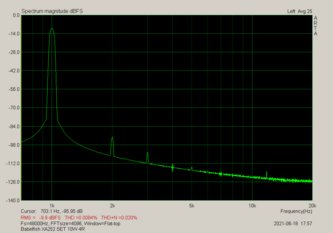

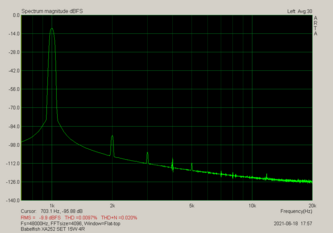

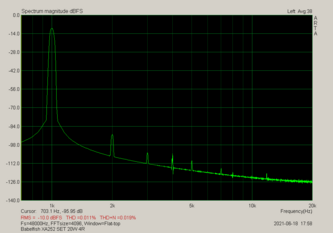

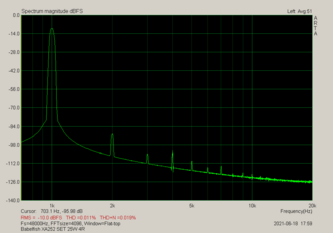

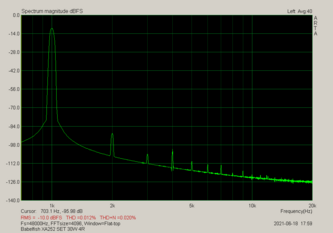

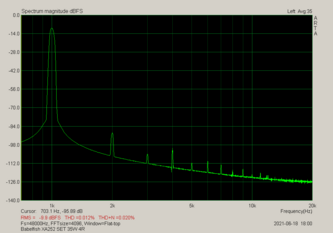

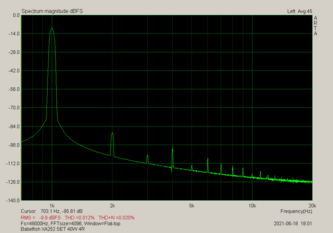

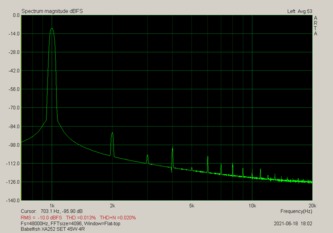

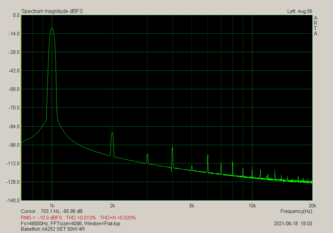

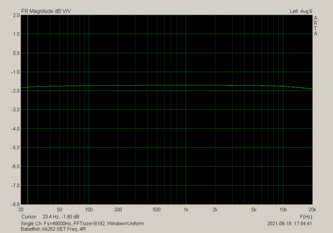

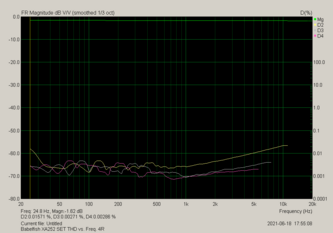

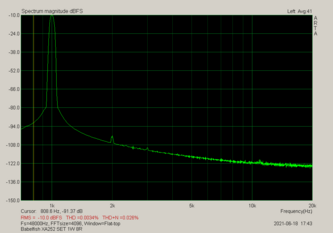

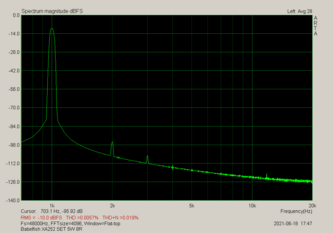

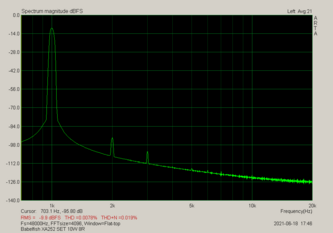

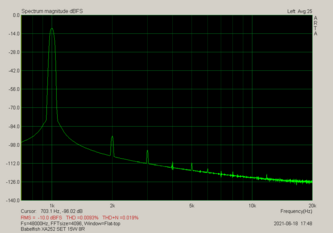

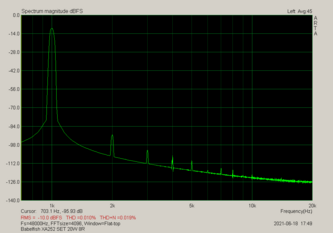

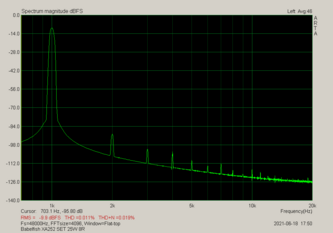

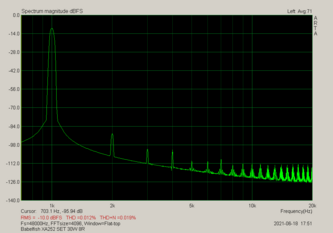

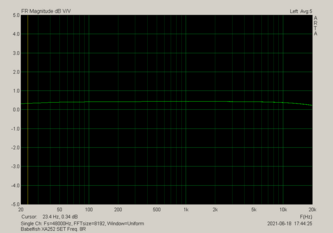

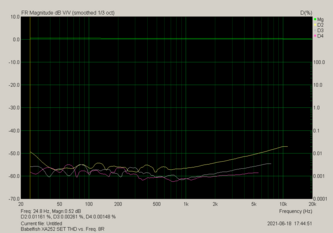

OK, I've compared graphs B. XA252 waaaaay down in THD at all power levels, so no real comparison, except same THD Spectra nature (that is more "except") then, THD levels comparison between B. XA252 SET and B. XA252 SIT clearly shows that SET is uniformly approx. 6db down at each tested power level in my book, that's pretty good emulation - achieving same behavior and consistency, while still making some desired difference ...... even ignoring that we are emulating nearly 100$ part (plus not so easy to obtain) with 25$ part edit: for SET - did I said that even famous ∀ Class DEF current distribution is clearly evident - Schade SIT emulation is working as proper SIT in DEF - I like to see it as SIT being error corrector for Mosfet -

Babelfish XA252 / Babelfish XA252 SIT/ Babelfish XA252 SET

Zen Mod je odgovorio/la Zen Mod's temus u Solid State

Babelfish XA252 SET - graphs , 4R load, BFR=22R everything the same, load changed to 4R that's it; my preference sez that I'm not even going to try tests with 510R for BFR as expected (ZM being lazy .......... I'm going to really check that maaaaybe later tonight, to actually compare graphs one by one) - this one being somewhere in the middle between B. XA252 and B. XA252 SIT -

Babelfish XA252 / Babelfish XA252 SIT/ Babelfish XA252 SET

Zen Mod je odgovorio/la Zen Mod's temus u Solid State

-

Babelfish XA252 / Babelfish XA252 SIT/ Babelfish XA252 SET

Zen Mod je odgovorio/la Zen Mod's temus u Solid State

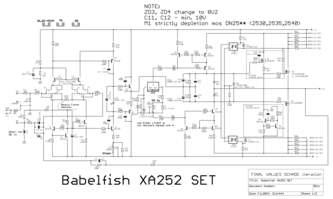

Babelfish XA252 SET as my pal Indra, member of same Pantheon and evidently same Caste to which I belongs, asked ....... here is schm of Babelfish XA252 SET fancyschmancy name for Schade iteration of full Mos OS, where upper output Mosfet is Schaded, so practically being emulation of SIT gate resistor R50 increased to 750R, introduced new resistor R58 (18K) SIT related parts (two rectangles of short dash lines) mounted - as for SIT iteration, but instead of M1 - IRF510 (we are using for SIT), placed DN2540 R46 changed to 33R we need around 3V voltage level at left (inner) side of R50, so result as is - DN2540 gate voltage is 3-4V-ish (fine tune of R46 possible to achieve full symmetry of M1 and M3 gate voltages, trivial task) ; these being referenced to output node all parts titles ref. to attached schm once when I have final pcb, containing all 3 amps , schmtcs with proper nomenclature will be posted I could avoid T8-Q9 30mA CCS, and route lower end of R46 to output node (M2 source), but as I already had CCS in place, why not using it yes, as Indra said - Papa's fave gigglywiggly graphs are saying that 2nd is neg. in phase ; that not posted, just simulated, but no reason for doubt -

Savica je milozvucna legenda

-

vec je oklopljen magnetski

-

Babelfish XA252 / Babelfish XA252 SIT/ Babelfish XA252 SET

Zen Mod je odgovorio/la Zen Mod's temus u Solid State

...... and I figured few tiny details, how to make Schade iteration now, just need few logic level TO220 mosfets , to put N pucks back ....... an will inform ya few days -

Babelfish XA252 / Babelfish XA252 SIT/ Babelfish XA252 SET

Zen Mod je odgovorio/la Zen Mod's temus u Solid State

Babelfish XA252 gives you all details .........so you can form your own Opinion Babelfish XA252 SIT gives you ready Opinion, with all details, and it doesn't care what you think go figure -

apsolutno je svejedno u sekvenci koji po redu relej se pali/gasi svodi se na: Relay N ON, delay xxmS, Relay N-1 Off

-

Babelfish XA252 / Babelfish XA252 SIT/ Babelfish XA252 SET

Zen Mod je odgovorio/la Zen Mod's temus u Solid State

have some workshop unrelated things today and tomorrow, so second visit to SSE, with Babelfish XA252 SIT is postponed for Thursday as I said, due to too much happenings (both in reality and in my head), I'm far from being capable of both critical and objective listening, thus need for visiting SSE however, as I completed both SIT channels on T-Bed 2 yesterday, couldn't resist today afternoon and I did some listening in my workshop Spoooooky and so much ball$$! dunno (as said) how's in comparison with anything (I need probably just time to re-set, peaceful time without making new ones) but it's as microscope size of Palomar ......... Rocking! sense of foundation and authority, as I remember, even greater than with 100W Babelfish Aleph XJ go figure ZM, Mad Hatter -

FW site, Articles page

-

to sto si dobio su po svoj prilici refurbished, naknadno punktovane duze nozice nije cudo ako je koji skiknuo, a braca Kinezi ne proveravadu testiranje - samo Nelsonov jig iz F3 Article

-

-

klikovi su od koda srecom mene Vinko naucio kako i gde, jer ja sam vec znao iz mehanicke verzije IPumpkina da mora make-before-break detalji su najvazniji, cudom , ne overall concept sto rece Vinko - ako to nije sve ispeglano, dzaba trud, bolje da nista nisi radio dakle samo sredi delays za otpustanje prethodnog relea i najo puc takodje obrati paznjui na Vpp signala, ne znam na kom nivou Muse pobudali davno je bilo kad sam se igrao sa tim

-

neces cuti razliku izmedju korektnog relejnog i Muse, ako je sve ostalo isto ja sam potrosio nedelju dana vremena, da bih to na kraju ustanovio sa druge strane, postoje trikovi implementacije .......... koje evidentno prepoznaje malo njih - msm prvenstveno na relejni atenuator no, ne moram ja bas za svaku sitnicu da se mecem ....... a tebi nece ni koristiti jer radis sa Muse opet, bitna je zabava, to sto rekoh je cisto sa teh. strane .... a znamo da se ne bavimo ovim samo zbog tehnike

-

svak radi ono sto zna evidentno logicari oce da imaju dobar preamp onda uzmu sto ne znaju, a preinzenjerisu sto znaju al neka, bitno da su srecni - sebi prave kako im se pravi ja, sto mi ni stap ne treba kao daljinac, nisam merodavan

-

Trenutno na sajtu 0 članova, 1 Skrivenih, 148 Gosta (Pogledaj celu listu)

- There are no registered users currently online

-

Forumska statistika

9.1k

Ukupan broj tema450.9k

Ukupan broj objava -

Statistika članovȃ